1. 레지스터 전송

1-1 여러 가지 RTL 표시방식

RTL 표시 방식은 위와 같이 Text RTL, VHDL, Verilog가 있으며, 각각 operation 기호가 다르다.

1-2 MUX를 활용한 전송 연결

source register가 여러 개 일때 MUX를 활용하여 연결해줄 수 있다. K1 : RO ←R1, K'K2 : R0 ←R2 를 구현한다고 할 때, 2x1 MUX를 이용하여 R0 앞에 MUX를 붙여 조건에 따라 R1 혹은 R2가 R0에 연결되도록 만들 수 있다.

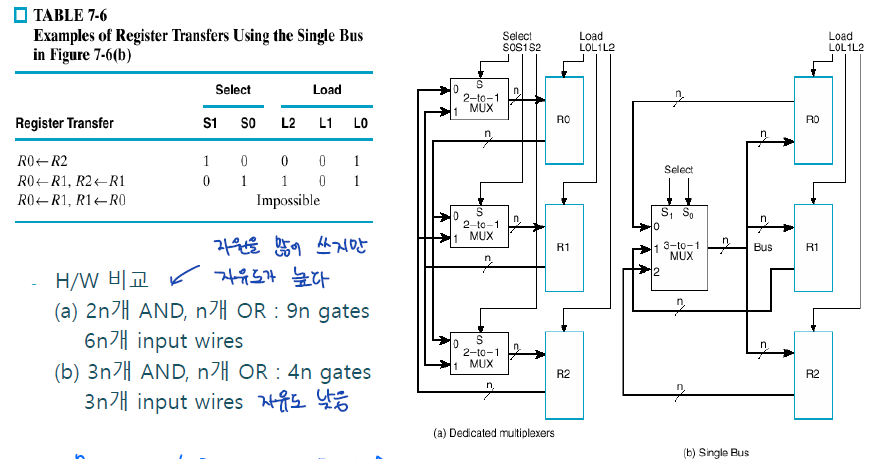

1-3 버스방식 전송 연결

(a) Dedicated Multiplexers 방식의 경우 자원을 많이 쓰지만 자유도가 높고 (b)single bus 방식의 경우 자원은 덜 사용하지만 자유도가 낮다.

2.데이터 처리 장치 (data path)

ALU : 마이크로 연산 실행 장치

구성 - 조합연산회로와 accumlator(reg)

실행시간 - 1uo/ 1ck

2 operand 입력, 1 출력

- CPU 주요 구성부

(1) data path 블록 - ALU, Shifter, Register, MUX, decoder, BUS연결회로 등

(2) 제어 신호 - uo를 수행하기 위한 적절한 신호 발생

간단히 그림에 대해 설명하자면, Decoder를 통해 Destination을 select할 수 있으며 이 신호와 load Enable 신호로 register를 select한다.

A select MUX를 통해 나온 Adata는 ALU로 들어오고, B data는 MUX로 통한다. 이 때 MB select가 0이면 B data가 ALU로, 1이면 constant in이 ALU로 들어간다. 이 MUX는 즉, 상수 계산 처리를 위해 존재한다. 특정 연산에 대한 instunction이 메모리 주소마다 저장되어 있다. G select 신호로 연산 종류를 선택하고, MF select에서는 ALU 출력을 내보낼지, Shift 출력을 내보낼지 정한다. 마지막으로 MUX D에서는 MD select로 F 값 혹은 메모리에서 나온 data값 중에 선택한다.

ex) R1 ← R2 + R3 구현

(1) A select = 10, R2를 A BUS에, B select=11, R3을 B BUS로 지정

(2) MB =0

(3) G → A+B연산 선택

(4) MF=0, ALU 출력선택

(5) MD=0, MUX F → D bus

(6) D select=01, 즉 R1 선택

(7) load enable=1, clock edge에서 R1에 값 저장

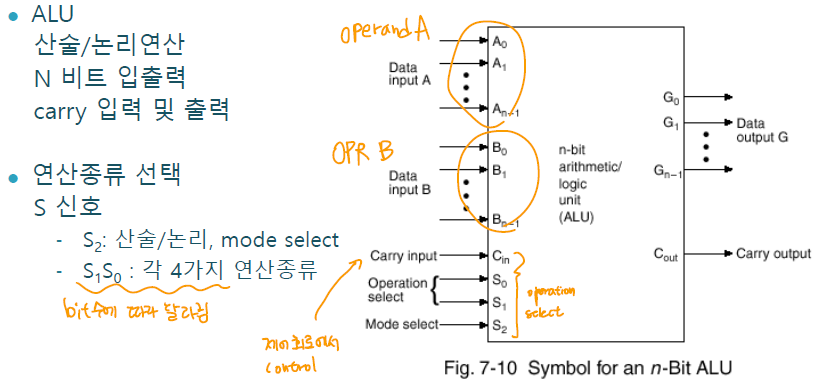

3. ALU 설계

data path의 Function unit 구성 요소 중 하나인 ALU 설계이다.

ALU 설계를 위해 산술/논리 연산 logic이 필요하다. 연산의 종류는 S 를 통해 select 된다.

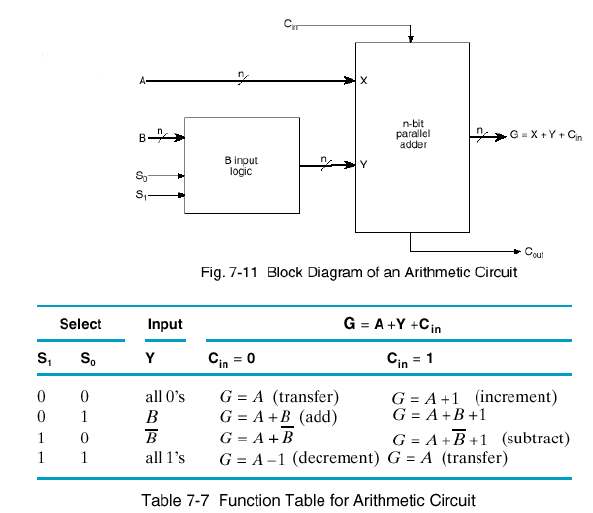

3-1 산술연산회로 설계

select 신호에 따라 Y값이 정해지고, output G는 input X, Y, Cin 값으로 결정된다. select신호와 B가 어떤 input logic을 통해 Y값이 결정되는지 아래의 그림에서 자세히 알 수 있다.

표를 보면 B값과 상관없이 S에 따라 Y값이 정해지는 것을 알 수 있고, 카르노 맵으로 식을 도출하면 오른쪽과 같이 input logic이 만들어진다.

3-2 논리연산회로 설계

S1S0에 의해 4개의 연산 중에 1개의 결과값이 output으로 출력되는 구조이다.

3-3 ALU 설계

위에서 만든 산술연산회로와 논리연산회로를 조합하여 ALU를 설계할 수 있다. 이 때 S2 신호로 두 연산 회로 중 원하는 연산회로를 선택할 수 있다. 따라서 최종적으로 S2 ~ S0신호와 Cin 으로 원하는 function을 구현하기 위한 Operation을 지정할 수 있다.

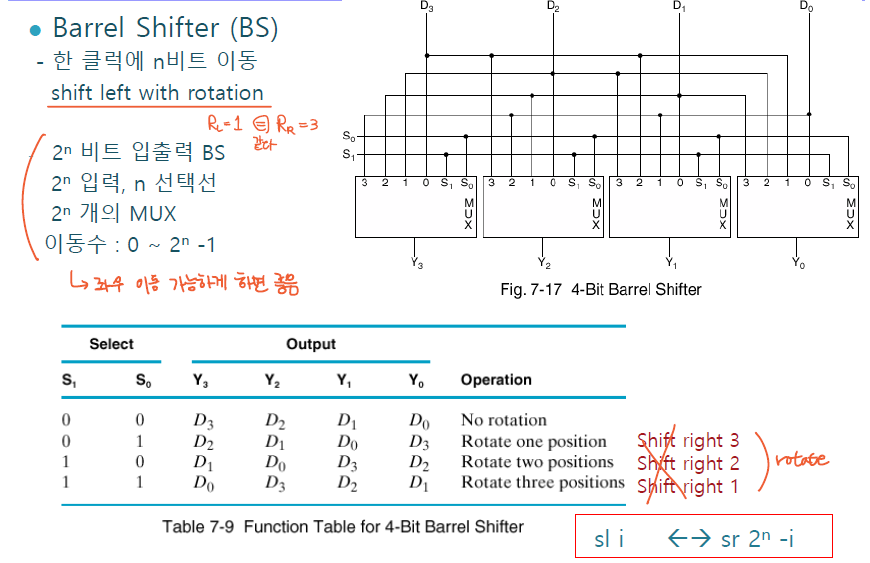

4. Shifter 회로

data path의 Function unit 구성 요소 중 하나인 Shifter 회로에 대한 설명이다.

S1S0 신호에 따라 hold/ Shift R/ Shift L 동작을 하는 회로이다. 위의 회로를 보면 S가 00일 때 각 MUX가 d0이 select되어 output으로 나간다. 이 경우 결국 원래 자리 그대로 비트가 출력되기 때문에 hold이다.

S가 01일때 d1이 select되어 output으로 나간다. 이 때 1bit씩 오른쪽으로 shift되고 맨 왼쪽 비트는 0이 채워진다. (IR값)

이 때 IR을 1'b0이 아닌 B0와 연결해준다면 rotate 기능이 된다.

S가 10일때 d2가 select되어 output으로 나간다. 즉 1bit씩 왼쪽으로 shift된 결과를 얻을 수 있다.

Barrel Shifter는 한 클럭에 n비트를 이동할 수 있는 shifter이다. 그림과 같이 회로가 구성되며 정확히는 shift라기보다 값이 rotate되는 구조이다.

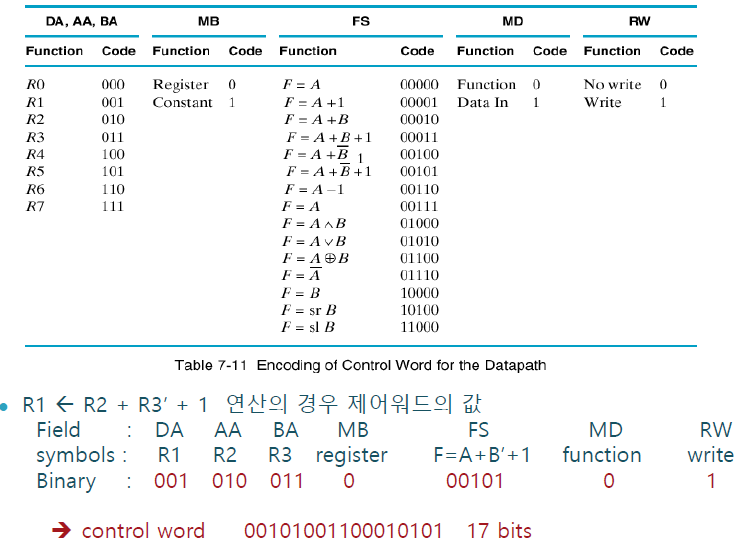

5. Control word 제어 워드

마이크로 연산의 데이터처리를 위해서는 적절한 제어신호들이 필요하다. 이를 제어 워드라고 하며, RW, MD, FS, MB, BA, AA, DA 로 구성되어 있다. 적절한 코드 값을 줌으로써 원하는 데이터 처리 및 동작이 가능하다.

예를 들어 위의 그림과 같이 제어 워드를 정할 수 있다. DA/AA/BA는 연산에 필요한 register를 정하고, MB는 B data를 constant로 할지 Register값으로 할지를 정한다. FS는 연산의 종류를, MD는 Function값을 내보낼지 메모리부터 온 Data In값을 내보낼지를, RW는 레지스터에 write여부를 정한다.

위의 예시를 통해 다양한 마이크로 연산을 위해 제어워드를 어떻게 지정해야 하는지 알 수 있다.

'[Harman교육] 베릴로그' 카테고리의 다른 글

| [23.03.22] CPU설계 - Shifter unit (0) | 2023.03.22 |

|---|---|

| [23.03.21] CPU 설계 - ALU unit (0) | 2023.03.21 |

| [23.03.17] 무어/ 밀리 모델 (0) | 2023.03.17 |

| [23.03.14] 조합회로와 순차회로 -2 (0) | 2023.03.16 |

| [23.03.13] 조합회로와 순차회로 -1 (0) | 2023.03.16 |